# Performance Comparisons of III–V and Strained-Si in Planar FETs and Nonplanar FinFETs at Ultrashort Gate Length (12 nm)

Seung Hyun Park, Student Member, IEEE, Yang Liu, Neerav Kharche, Member, IEEE, Mehdi Salmani Jelodar, Student Member, IEEE, Gerhard Klimeck, Senior Member, IEEE, Mark S. Lundstrom, Fellow, IEEE, and Mathieu Luisier

Abstract—The exponential miniaturization of Si complementary metal-oxide-semiconductor technology has been a key to the electronics revolution. However, the downscaling of the gate length becomes the biggest challenge to maintain higher speed, lower power, and better electrostatic integrity for each following generation. Both industry and academia have been studying new device architectures and materials to address this challenge. In preparation for the 12-nm technology node, this paper assesses the performance of the In<sub>0.75</sub>Ga<sub>0.25</sub>As of III-V semiconductor compounds and strained-Si channel nanoscale transistors with identical dimensions. The impact of the channel material property and the device architecture on the ultimate performance of ballistic transistors is theoretically analyzed. Two-dimensional and three-dimensional real-space ballistic quantum transport models are employed with band structure nonparabolicity. The simulation results indicate three conclusions: 1) the In<sub>0.75</sub>Ga<sub>0.25</sub>As FETs do not outperform strained-Si FETs; 2) triple-gate Fin-shaped Field Effect Transistor (FinFET) surely represent the best architecture for sub-15-nm gate contacts, independently from the material choice; and 3) the simulations results further show that the overall device performance is very strongly influenced by the source and drain resistances.

Index Terms—Double gate, finFETs, III-V versus Si, InGaAs, metal-oxide-semiconductor FETs, real-space effective mass simulations, single gate, strained-Si, triple gate.

# I. INTRODUCTION

OVEL materials and device architectures that will outperform conventional Si-based FETs at ultrascaled dimensions are required to keep improving the performance of nanoscale transistors [1]–[17]. In particular, it has been demon-

Manuscript received February 16, 2012; revised April 25, 2012; accepted April 27, 2012. Date of publication May 18, 2012; date of current version July 19, 2012. This work was supported in part by MSD Focus Center, one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity and support from Intel Corporation. The review of this paper was arranged by Editor J. D. Cressler.

S. H. Park, M. Salmani-Jelodar, G. Klimeck, and M. S. Lundstrom are with the Network for Computational Nanotechnology, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA (e-mail: park43@purdue.edu).

Y. Liu is with the IBM Research, Hopewell Junction, NY 12533 USA.

N. Kharche is with the Computational Center for Nanotechnology Innovations, Rensselaer Polytechnic Institute, Troy, NY 12180 USA.

M. Luisier was with the Network for Computational Nanotechnology, School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA. He is now with the Integrated Systems Laboratory, ETH Zürich, 8092 Zürich, Switzerland (e-mail: mluisier@iis.ee.ethz.ch).

Digital Object Identifier 10.1109/TED.2012.2198481

strated that InGaAs FETs can exhibit performance superior to Si FETs because of their very high-electron mobility. This may enable high-speed and low-power logic applications beyond Si CMOS technology [2], [4], [8]–[10], [14]–[20]. However, due to recent innovations in strain engineering, which have boosted its electron and hole mobility, Si is still the most popular material and is widely used as the CMOS channel material in industry [6], [21], [22].

A significant challenge associated with the downscaling of transistors is the poor electrostatic control of a single-gate contact over the channel of ultrascaled devices calling short-channel effects (SCEs). Multigate architectures [2], [3], [8], [11], [23]–[25], as recently introduced by Intel for the 22-nm technology node [26], can help suppress SCE, even at short gate lengths; deliver near-ideal subthreshold slopes; and reduce drain-induced barrier lowering (DIBL) [2], [3].

In preparation for the 12-nm technology node, this paper investigates the performance of single-/double-gate planar ultrathin-body (UTB) FETs and triple-gate FinFETs employing  $In_{0.75}Ga_{0.25}As$  as a channel material and compares them to strained-Si channel FETs. The high- $\kappa$  gate dielectric HfO<sub>2</sub> is used as an insulator to circumvent the gate leakage current caused by tunneling across the gate oxide [8], [10], [16], [17], [27].

Since fabricating III–V and Si nanoscale transistors with identical dimensions and electrical properties is very difficult, time-consuming, and expensive, the performance of all the devices considered in this paper are simulated using a state-of-the-art computer-aided design tool [16], [17], [18], [27]–[31] and not extracted from an experimental setup. Numerical device simulations provide a comprehensive way to capture the electrical behavior of different devices with different materials and structures for performance assessment as long as the same set of approximations is used in all cases.

The theoretical modeling of 2-D and 3-D nanoscale transistors demands a proper treatment of quantum effects such as the energy-level quantization caused by strong quantum confinement of electrons and band structure nonparabolicity. To address these issues, a multidimensional quantum transport solver based on a self-consistent solution of the Schrödinger and Poisson equations in the real-space effective mass approximation [19] with a tight-binding (TB) extraction of the effective mass values is used to simulate III–V and strained-Si devices in

planar and nonplanar architectures [18], [28]. With this simulation approach, the I-V characteristics of realistic III–V high-electron mobility transistors could be accurately reproduced [16]–[19]. Electron–phonon scattering [29], surface roughness [30], alloy disorder [31], and tunneling gate leakage [27] can be included, in principle, in the simulations. However, they are not included due to high computation cost in real-space modeling, and all the FETs are simulated in the ballistic limit of transport.

This paper is organized as follows. Section II describes the single-/double-gate planar UTB FETs and triple-gate FinFET structures and introduces the simulation approach. The performance of devices employing  $In_{0.75}Ga_{0.25}As$  and strained-Si channels are compared and analyzed in Section III. Finally, Section IV summarizes the main findings of this paper and concludes it.

## II. DEVICE DESCRIPTION AND SIMULATION APPROACH

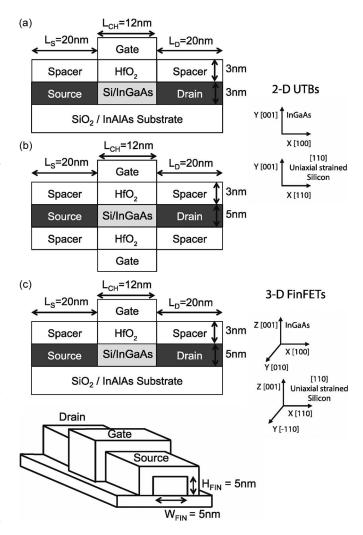

The device schematics of the single-/double-gate UTB FETs and triple-gate FinFETs modeled in this paper are shown in Fig 1. An  $\rm In_{0.75}Ga_{0.25}As$  layer on an  $\rm In_{0.52}Al_{0.48}As$  buffer is used as the channel material for III–V FETs [14]–[17]. The source and drain regions are n-doped with a donor concentration  $N_D=5\times 10^{19}~\rm cm^{-3}$  and a length of 20 nm. Transport occurs along the  $\langle 100\rangle$  crystal axis. A 1% uniaxial stress is applied to the  $\langle 110\rangle$ -oriented Si channels with a SiO<sub>2</sub> substrate. Strain is used to achieve a higher electron velocity resulting from a reduction of the effective mass  $m^*$  parallel to the stress direction [6], [21], [22]. The source and drain regions of the Si transistors are n-doped with a donor concentration  $N_D=1\times 10^{20}~\rm cm^{-3}$  and a length of 20 nm.

All architectures use an HfO<sub>2</sub> high- $\kappa$  gate stack with a relative dielectric constant  $\varepsilon_R=20$ , a thickness  $t_{\rm OX}=3$  nm, and a conduction-band gap offset  $\Delta E_C=2.3$  and 2.48 eV for In<sub>0.75</sub>Ga<sub>0.25</sub>As and Si, respectively [32], [33]. This corresponds to an equivalent oxide thickness (EOT) of 0.585 nm, which is consistent with the International Roadmap for Semiconductors (ITRS) specifications for the 12-nm technology node [1]. The source and drain regions are covered by spacers made of a low dielectric material ( $\varepsilon_R=5$ ) to reduce the electric fields coupling to the gate.

The simulated III–V and Si UTB FET and FinFET devices have the same geometry and gate stacks but different channel materials and doping concentrations. The OFF-state current of all the devices is set to  $0.1~\mu\text{A}/\mu\text{m}$  by varying the work function of the metal gate contact.

To reduce the computational burden, the device structures are simulated in two steps. First, only the intrinsic domain, as illustrated in Fig. 1, is considered. Then, the source  $(R_S = 80~\Omega \cdot \mu \text{m})$  and drain  $(R_D = 80~\Omega \cdot \mu \text{m})$  series resistances taken from the ITRS are added in a postprocessing step to the intrinsic I-V characteristics. This procedure was previously described in [16] and [17].

The real-space quantum transport solver OMEN is used to simulate the 2-D and 3-D FETs in Fig. 1 in the ballistic transport regime. The Schrödinger and Poisson equations are self-consistently solved using the effective mass approximations and a finite difference grid. To account for the strong

Fig. 1. Schematics of the simulated devices. (a) Single-gate planar UTB FET. (b) Double-gate planar UTB FET. (c) 2-D and 3-D schematics of a triple-gate FinFET.

nonparabolicity of III–V materials, the effective masses of the  $In_{0.75}Ga_{0.25}As$ -based transistors are extracted from a  $sp^3d^5s^*$  TB band structure calculation including spin–orbit coupling [14]–[17].

The transport effective masses  $m_t$  for the  $\rm In_{0.75}Ga_{0.25}As$  transistors are obtained by fitting the curvature of the lowest TB conduction band with a parabola. The confinement effective masses  $m_c$  are chosen so that the energy difference between the two lowest TB conduction bands is correctly reproduced by the effective mass model. The layers around the  $\rm In_{0.75}Ga_{0.25}As$  channel are taken into account when the effective masses are extracted from the TB band structure so that the electron wave function can deeply penetrated into them, resulting into a larger transport effective masses. This method delivers structure-dependent effective masses, which are quite different from their bulk value, yet are in good agreement with experimental data [16], [17].

There are two sets of effective masses for the stained-Si devices with transport along the  $\langle 110 \rangle$  crystal axis covering the sixfold-degenerate valleys of Si. First, there is a group of fourfold-degenerate valleys with the same transport and confinement effective masses extracted as in [34] and [35].

| TABLE I                                                          |

|------------------------------------------------------------------|

| TRANSPORT AND CONFINEMENT EFFECTIVE MASSES AND SUBBAND           |

| Degeneracy for the $In_{0.75}Ga_{0.25}As$ and Strained-Si Planar |

| LITE FETS AND TRIPLE-GATE NONDLANAR FINEFTS                      |

| Architecture | Channel Material                         | $m_X$  | $m_Y$  | $m_Z$  | Degeneracy |  |

|--------------|------------------------------------------|--------|--------|--------|------------|--|

| Single-gate  | In <sub>0.75</sub> Ga <sub>0.25</sub> As | 0.066  | 0.0159 | 0.066  | 1          |  |

| UTB FETs     | [110] 1% Uniaxial                        | 0.16   | 0.9    | 0.22   | 2          |  |

| 2-D          | Strained Silicon                         | 0.5    | 0.19   | 0.31   | 4          |  |

| Double-gate  | In <sub>0.75</sub> Ga <sub>0.25</sub> As | 0.059  | 0.0109 | 0.059  | 1          |  |

| UTB FETs     | [110] 1% Uniaxial                        | 0.16   | 0.9    | 0.22   | 2          |  |

| 2-D          | Strained Silicon                         | 0.5    | 0.19   | 0.31   | 4          |  |

| Triple-gate  | In <sub>0.75</sub> Ga <sub>0.25</sub> As | 0.0706 | 0.0769 | 0.0769 | 1          |  |

| FinFETs      | [110] 1% Uniaxial                        | 0.16   | 0.22   | 0.9    | 2          |  |

| 3-D          | Strained Silicon                         | 0.5    | 0.31   | 0.19   | 4          |  |

Since the corresponding energy quantization levels are relatively high in energy, strain is not considered for these bands. The second group of two-fold-degenerate valleys requires more attention because the application of a uniaxial tensile stress strain strongly influences the value of their transverse effective masses, which strongly decreases, leading to better transport properties. The effective masses in this case were taken from [21] and were verified using the Vienna Ab-Initio Simulation Package [36]. All the effective masses used in this paper are summarized in Table I.

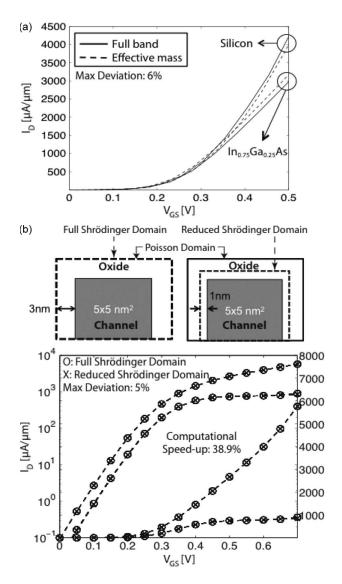

Full-band atomistic simulations are too computationally expensive to be applied to the complete full I-V characteristics of large 3-D device structures, as shown in Fig. 1. However, to verify that our method that extracts effective masses from TB band structures works well, the intrinsic  $I_D$ - $V_{GS}$  of the In<sub>0.75</sub>Ga<sub>0.25</sub>As and strained-Si 3-D FinFETs are simulated in the effective mass approximation and compared with the atomistic TB model [28] at a single  $V_{DS} = 0.7$  V. The results in Fig. 2(a) show that both methods exhibit identical trends with values of drain current very close to each other when  $I_D$  < 3000  $\mu$ A/ $\mu$ m. This corresponds to the domain of interest and demonstrates that a simulation approach based on the effective mass approximation can be used when it is well calibrated against a full-band model. We note here again that the effective masses used for such agreement are significantly different from the bulk values and heavily influenced by device geometry and confinement details. The use of uncalibrated bulk-based effective masses would yield significantly different results and would not enable a realistic comparison between the Si and InGaAs material systems.

Apart from the band structure model, another severely limiting factor in the simulation of 3-D FinFETs is the size of their cross section, which increases the solution time for the Schrödinger equation in real space. While the entire cross section needs to be included to solve the Poisson equation, the simulation domain of the Schrödinger equation can be indeed reduced. The electron wave function does not extend all along the surrounding dielectric layers, and the Schrödinger domain can be therefore restricted to 1 nm around the  $\rm In_{0.75}Ga_{0.25}As$  and Si channels. This is illustrated in Fig. 2(b). The  $I_D - V_{GS}$

Fig. 2. (a) Basis reduction: comparison of the full-band (solid lines) and effective mass (dashed lines)  $I_D$ – $V_{GS}$  characteristics at  $V_{DS}=0.7~{\rm V}$  (b) Domain reduction: comparison of  $I_D$ – $V_{GS}$  characteristics of the strained-Si FinFET at  $V_{DS}=0.05~{\rm V}$  and  $V_{DS}=0.7~{\rm V}$  simulated using the entire Fin cross section (crosses) and reduced spatial domain that captures the wave function leakage (circles).

transfer characteristics of the strained-Si FinFET at  $V_{DS} = 0.05$  and 0.7 V are shown in Fig. 2(b) in logarithmic and linear scale. A maximum deviation between the full and the reduced Schrödinger domain solutions of 5% is observed. Consequently, by reducing the simulation domain for the Schrödinger equation, the simulation time for the whole  $I_D$ - $V_{GS}$  characteristics consistent of 16 bias points decreases about 39% from 90–55 h on 256 cores on a 2.5-GHz quad-core AMD 2380 processors [37].

# III. RESULTS AND DISCUSSION

Based on the methodology presented in Section II, we have simulated the III–V and strained-Si UTB FETs and FinFETs shown in Fig. 1. From the resulting transfer  $I_D$ – $V_{GS}$  and output  $I_D$ – $V_{DS}$  characteristics, some key technology parameters such as, SS, DIBL, ON-state current  $I_{\rm ON}$ , ballistic injection velocity

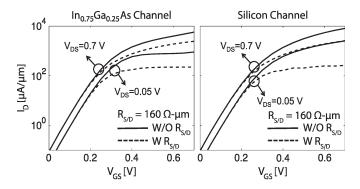

Fig. 3. Intrinsic (solid lines) and extrinsic (dashed lines)  $I_D - V_{GS}$  characteristics of triple-gate FinFETs for (a)  ${\rm In}_{0.75}{\rm Ga}_{0.25}{\rm As}$  and (b) strained-Si channels.

$(V_{\mathrm{INJ}})$ , and inversion charge density  $N_{\mathrm{INV}}$  were extracted for each device.

As explained earlier, the source and drain contact regions extending beyond the intrinsic device are excluded from the quantum transport simulation. These extrinsic source and drain regions are characterized by two series resistances ( $R_S$  and  $R_D$ ) included as a postprocessing step where the intrinsic  $V_{GS,\rm in}^*=V_{GS,\rm ext}-I_DR_S$  and  $V_{DS,\rm in}^*=V_{DS,\rm ext}-I_D(R_S+R_D)$  account for the correction. For example, the simulated on-state current of the  $\rm In_{0.75}Ga_{0.25}As$  triple-gate FinFET is extracted at  $V_{GS}=V_{DS}=0.7$  V and amounts to  $I_{\rm ON}/W=2490~\mu A/\mu m$ , but the intrinsic biases are  $V_{GS,\rm in}=0.5$  V, and  $V_{DS,\rm in}=0.3$  V with  $R_S=80~\Omega\cdot\mu m=R_D=80~\Omega\cdot\mu m$ . This method has been applied previously and showed good agreement with experimental data [16]–[19]. Note that drain current of the triple-gate FinFET is normalized by the fin height of  $\rm H_{Fin}=5~nm$  [38].

Fig. 3 shows the intrinsic  $I_D-V_{GS}$  and the postprocessed  $I_D-V_{GS}$  transfer characteristics of the  $In_{0.75}Ga_{0.25}As$  and strained-Si triple-gate FinFETs at  $V_{DS}=0.05~\rm V$  and  $V_{DS}=0.7~\rm V$ . The source and drain series resistances have a negligible effect on the OFF state, but they significantly reduce the drain current in the ON state, by more than 50% in both FETs: The ON-state current of the  $In_{0.75}Ga_{0.25}As$  triple-gate FET decreases from 5768 to 2490  $\mu A/\mu m$  after the postprocessing. It is clear that the extrinsic source and drain contact regions dominate the overall performance of both device types. Hence, careful and low resistance of contact designs may turn out to be even more important than the optimization of the central device in future device architectures, regardless of the channel material.

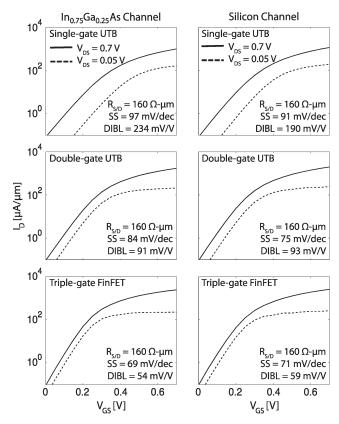

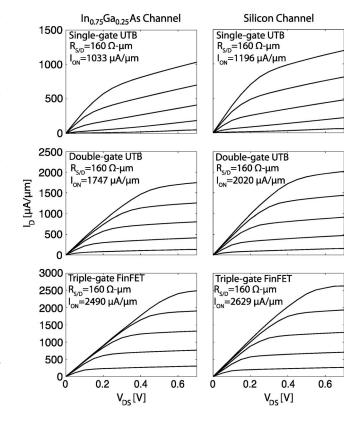

Figs. 4 and 5 show the ballistic transfer and output characteristics of the simulated devices after the inclusion of the series resistances. All the performance parameters (SS, DIBL,  $I_{\rm ON}$ ,  $V_{\rm INJ}$ , and  $N_{\rm INV}$ ) are extracted from the I-V characteristics shown in Figs. 4 and 5. The values are reported in Table II, where the effect of the contact series resistances are taken into account. The power supply voltage for each device is set to 0.7 V to meet the ITRS ON-state current requirements for III–V and Si devices [1], [9], and the metal gate work functions are tuned to obtain the same OFF-state current ( $I_{\rm OFF}=0.1~\mu{\rm A}/\mu{\rm m}$ ). Note that, for the single-gate transistors, a body thickness  $T_{\rm body}$  of 3 nm is needed because severe SCEs are observed with  $T_{\rm body}=5$  nm.

Fig. 4.  $I_D$ – $V_{GS}$  characteristics for the In $_{0.75}$ Ga $_{0.25}$ As and strained-Si FETs for two given drain voltage  $V_{DS}=0.05$  V and  $V_{DS}=0.7$  V with different gate voltages  $V_{GS}$  from 0.0 to 0.7 V (steps of 0.05 V) in semilog scale.

Fig. 5.  $I_D$ – $V_{DS}$  characteristics of the In $_{0.75}$ Ga $_{0.25}$ As and strained-Si FETs at six different gate voltages  $V_{GS}=0.0$  V, 0.3, 0.4, 0.5, 0.6, and 0.7 V.

| TABLE II                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------|

| DEVICE PERFORMANCE PARAMETERS FOR THE $In_{0.75}Ga_{0.25}As$ and Strained-Si in Single-/Double-Gate Planar FET       |

| and Triple-Gate FinFET Configuration. The Power Supply Voltage $V_{DD}$ for Each Device Is Set to 0.7 V,             |

| AND THE OFF-STATE CURRENT $I_{OFF}$ is Set to 0.1 $\mu A/\mu m$ . SS is Observed for the Saturated Value of $V_{GS}$ |

| Structure                     | Single-gate          |                      | Double-gate          |                      | Triple-gate          |                      |

|-------------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| Material                      | InGaAs               | Si                   | InGaAs               | Si                   | InGaAs               | Si                   |

| SS [mV/dec]                   | 97                   | 91                   | 84                   | 75                   | 69                   | 71                   |

| DIBL [mV/V]                   | 234                  | 190                  | 91                   | 93                   | 54                   | 59                   |

| <i>I<sub>ON</sub></i> [μΑ/μm] | 1033                 | 1196                 | 1747                 | 2020                 | 2490                 | 2629                 |

| $V_{INJ}$ [cm/s]              | 3.3×10 <sup>7</sup>  | 1.1×10 <sup>7</sup>  | 4.5×10 <sup>7</sup>  | 9.5×10 <sup>6</sup>  | 4.7×10 <sup>7</sup>  | 1.1×10 <sup>7</sup>  |

| $N_{INV}$ [/cm <sup>2</sup> ] | 1.5×10 <sup>12</sup> | 5.7×10 <sup>12</sup> | 2.1×10 <sup>12</sup> | $1.1 \times 10^{13}$ | 3.7×10 <sup>12</sup> | 1.8×10 <sup>13</sup> |

For example, the  $In_{0.75}Ga_{0.25}As$ -based single-gate FET shows an SS of 148 mV/dec and DIBL of 441 mV/V when  $T_{\rm body}=5$  nm, whereas these values are reduced to 97 mV/dec and 234 mV/V when  $T_{\rm body}=3$  nm. In addition, to maintain a full substrate depletion in the single-gate structure, the body thickness should be about 1/3 of the gate length. In the case of double-gate and triple-gate transistors, the same body thickness ( $T_{\rm body}=5$  nm) is employed for comparison under the same conditions. From the extracted performance parameters, the impact of the channel material property and device architecture on the ultimate performance of ballistic transistors is theoretically examined.

Most III–V compound semiconductors such as  $In_{0.75}Ga_{0.25}As$  ( $E_G=0.53$  eV,  $m^*=0.032$  m<sub>0</sub>, and  $\varepsilon_R=14.4$ ), InAs ( $E_G=0.36$  eV,  $m^*=0.023$  m<sub>0</sub>, and  $\varepsilon_R=15.15$ ), and InSb ( $E_G=0.18$  eV,  $m^*=0.014$  m<sub>0</sub>, and  $\varepsilon_R=16.8$ ) have a significantly lower band gap  $E_G$  and smaller electron effective mass  $m^*$ , as well as higher relative dielectric constant  $\varepsilon$ , than Si. These properties make devices employing III–V materials more prone to SCEs compared with Si. Multigate architectures become important to reduce SCEs in ultrascaled devices, particularly for III–V materials.

As shown in Table II, SCEs are significantly suppressed in terms of SS and DIBL in multigate structures, whereas single-gate structures cannot achieve decent performance parameters, even with a 3 nm of body thickness: Planar double-gate structures lead to an SS improvement of about 13% for the  $In_{0.75}Ga_{0.25}As$  FET and 18% for the strained-Si FET, as compared with the single-gate devices. The SS of the triplegate FinFET is improved by about 29% for the  $In_{0.75}Ga_{0.25}As$  FET and about 22% for the strained-Si FET, as compared with their single-gate planar counterparts.

More impressive results are the improvements of DIBL when going from planar single-gate to planar double-gate structures and nonplanar triple-gate FinFETs: For the  $In_{0.75}Ga_{0.25}As$  FET, DIBL decreases from 234 (single gate) to 91 mV/V (double gate) and further down to 54 mV/V when used as a FinFET. In strained-Si, the same trend can be observed. DIBL is reduced from 190 to 93 mV/V for the double-gate structures and finally down to 59 mV/V for the triple-gate FinFET. From these results, it can be concluded that only multigate structures, particularly triple-gate FinFETs, provide a good enough electrostatic channel control and minimize the

Fig. 6. (a) DIBL. (b) Geometric screening length ( $\lambda$ ) of the In<sub>0.75</sub>Ga<sub>0.25</sub>As and strained-Si planar and nonplanar FETs.

SCEs as the transistor gate lengths are scaled down below the 15-nm technology node.

The observed trends in DIBL in Fig. 6(a) can be explained by invoking the concept of the geometric screening length for fully depleted silicon-on-insulator MOSFETs in [39]. The geometric screening length ( $\lambda$ , in nanometers) is used as a measure of SCEs inherent to a device structure [11], [22], [40]. It describes the electrostatic controllability of the depletion region in the channel. The SCEs are proportional to the geometric screening length. A shorter geometric screening length reduces the influence of the drain contact on the channel region and suppresses SCEs. In addition, an increased number of gates with the same dimension of body thickness  $T_{\rm Body}$  and oxide thickness  $T_{\rm OX}$  reduce the geometric screening length, as shown in (1) [11],

[20], where the subscript of each  $\lambda$  represents the number of gates as follows:

$$\lambda_{1} = \sqrt{\frac{\varepsilon_{\text{Body}}}{\varepsilon_{\text{OX}}} T_{\text{Body}} T_{\text{OX}}} \quad \lambda_{2} = \sqrt{\frac{\varepsilon_{\text{Body}}}{2\varepsilon_{\text{OX}}} T_{\text{Body}} T_{\text{OX}}}$$

$$\lambda_{3} = \sqrt{\frac{\varepsilon_{\text{Body}}}{3\varepsilon_{\text{OX}}} T_{\text{Body}} T_{\text{OX}}}.$$

(1)

Fig. 6(b) illustrates the behavior of the geometric screening length in the  $In_{0.75}Ga_{0.25}As$  FET and strained-Si single-, double-, and triple-gate devices. As it can be seen, the nonplanar triple-gate FinFET exhibit the lowest geometric screening length and best electrostatic control among all three architectures in terms of SS and DIBL. The behavior of the geometric screening length also captures the higher improvement rate of SCEs in the  $In_{0.75}Ga_{0.25}As$  transistors as the number of gates increases. Indeed, the difference between the geometric screening length of the  $In_{0.75}Ga_{0.25}As$  and strained-Si FETs  $(\Delta\lambda_{\rm number\ of\ gates}=|\lambda_{\rm InGaAs}-\lambda_{\rm Silicon}|)$  decreases as the number of gates increases, showing that III–V FETs see a larger benefit from multigate structures than Si FETs.

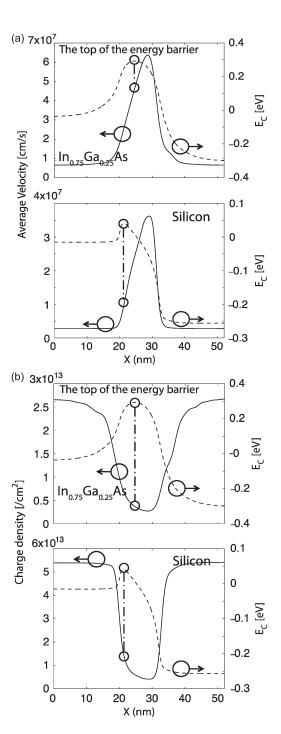

In addition to the electrostatic control, the properties of the channel materials strongly influence the performance of different FETs. The injection velocity at the top-of-the-barrier (ToB)  $V_{\rm INJ}$  provides a remarkable insight into the transport properties of a given transistor design [41]. Fig. 7 summarizes the method to extract this metric from quantum transport simulations. The In $_{0.75}$ Ga $_{0.25}$ As transistors benefit from a significantly smaller transport effective mass compared with strained-Si, as summarized in Table I, resulting in a ballistic injection velocity at the top of the potential barrier 3 to 4.7 times higher than strained-Si, depending on the device architecture.

However, due to the low effective mass, III–V FETs suffer from a lower density of states, which generally reduces the effective gate capacitance and the maximum achievable inversion charge density  $N_{\rm INV}$ . Under the same bias condition, the strained-Si transistors exhibit a 3.8 to 5.2 times higher inversion charge density at the ToB compared with the  ${\rm In}_{0.75}{\rm Ga}_{0.25}{\rm As}$  transistors. The increase in the inversion charge at the ToB overwhelm the benefit of a high injection velocity since the drain current can be expressed as  $I_D=qV_{\rm INJ}N_{\rm INV}$ , where q is the elementary charge. Therefore, the strained-Si FETs have slightly higher ballistic ON-state currents than the  ${\rm In}_{0.75}{\rm Ga}_{0.25}{\rm As}$  FETs, as shown in Table II.

The inversion charge and injection velocity are not only affected by material properties but also by the device architecture. In Table II, an increase in the injection velocity and inversion charge density can be observed in multigate architectures, which deliver higher current drives than single-gate devices. Hence, the ON-state current of the double-gate structures is improved by about 1.7 times in both the  $In_{0.75}Ga_{0.25}As$  and strained-Si FETs, as compared with the single-gate structures. The ON-state current of the triple-gate FinFET increases about 2.4 times in the  $In_{0.75}Ga_{0.25}As$  FET and 2.2 times in the strained-Si FET again compared with the single-gate architectures.

Fig. 7. (a) Ballistic injection velocity in the  $In_{0.75}Ga_{0.25}As$  and strained-Si double-/triple-gate FinFETs extracted at the top of the energy barrier (b) ON-state carrier density in the  $In_{0.75}Ga_{0.25}As$  and Si double-/triple-gate FinFETs extracted at the top of the energy barrier.

The  $In_{0.75}Ga_{0.25}As$  FETs see a higher performance improvement than the strained-Si in devices as the number of gates increases because the III–V materials are more sensitive to SCEs and take advantage of the better electrostatic control provided by the multigate architecture. As a consequence, this is a key finding of this paper; Table II demonstrates that the  $In_{0.75}Ga_{0.25}As$  and strained-Si triple-gate FinFETs exhibit almost identical performance metrics, i.e., a low SS and DIBL, as well as a large ballistic ON-state current.

However, it should be emphasized that the ballisticity of ultrashort III–V and strained-Si nanotransistors is currently unknown and is difficult to estimate. So far, Si-based FETs have always operated at about 50% of their ballistic limit, mainly due to surface roughness scattering at the Si-SiO<sub>X</sub> interface [42]. This number has not changed much for many successive technology generations. In addition, recent results of Si and III–V transistor simulations prove that electron–phonon scattering plays a more important role in Si than in III–V [43] because many more subbands are available in Si than in III–V for electrons to scatter out of the original state.

In contrary, specific III-V FETs seem to operate very close to their ballistic limit [16], [17], [19], [40] since surface roughness scattering is extremely small in these devices. In particular, growing a high- $\kappa$  layer directly on the top of a III-V channel might significantly increase surface roughness and remote Coulomb impurity scattering in these transistors and deteriorate their ballisticity. There are number of proposed processing techniques, such as interfacial passivation layer and atomic layer deposition to address the interfacial chemistry on III-V compound semiconductors [2], [10], [44]. In effect, their insulator layer is often made of another III-V material with a larger band gap or a wide-band-gap III–V material/high- $\kappa$  gate stack so that the channel-insulator interface is very smooth. Such insulator layers work well for relatively large EOT, but it is not clear yet what will happen when the EOT must be reduced below 1 nm.

It should also be noted that simulation results are based on the same low series resistance assumed in the In<sub>0.75</sub>Ga<sub>0.25</sub>As and strained-Si FETs simulation. The contacts of FETs based on III-V semiconductors are often characterized by higher series resistance compared with Si [8], [16], [17], [19], [40], [47]. However, some studies indicate that the contact resistance of n-type InGaAs can be significantly reduced by using innovative processing techniques [45], [46]. Experimentally, the contacts of III-V semiconductors have always been characterized by much larger series resistances than those of Si due to structural reasons [8], [9], [16], [17], [19], [40], [47]. The analysis presented here emphasizes the need to optimize the extrinsic part of the device by incorporating such novel processing techniques in order to reduce the contact resistance and improve the performance of III-V FETs [8], [45]–[47].

Since the exact ballisticity of the In<sub>0.75</sub>Ga<sub>0.25</sub>As and strained-Si FETs as well as the achievable contact series resistances are uncertain yet, it is difficult to determine what will be the best material for nanoscale transistors. However, numerical device simulations are required to provide performance projections according to the ITRS specifications without complicated fabrication processes of multiple device prototypes. The simulation results indicate that at gate length of 12 nm, In<sub>0.75</sub>Ga<sub>0.25</sub>As FETs deliver very similar performance as strained-Si FETs. The contact resistances dominate the behavior of both device types. Triple-gate Fin-FETs surely represent the best architecture for sub-15-nm gate contacts, independently from the choice of the channel material.

## IV. CONCLUSION AND OUTLOOK

This paper has assessed the performance of the  $In_{0.75}Ga_{0.25}As$  and strained-Si channel nanoscale transistors in single-/double-gate planar FETs and nonplanar triplegate FinFETs configurations in preparation for the 12-nm technology node. The device structure, doping concentration, OFF-state current, and normalization conditions are defined according to the ITRS specifications and with the help of Intel Corporation. The impact of the channel material property and device architecture on the ultimate performance of ballistic transistors is theoretically analyzed.

The simulation results indicate that III-V FETs do not outperform Si FETs in the ballistic regime but deliver very similar performance. However, III-V FETs is still one of the most promising candidates because they could operate closer to their ballistic limit than Si FETs under certain circumstances and therefore provide higher ON-state current due to less performance degradation from electron-phonon and surface scatterings. Ultrashort III-V FETs need multigate structures to overcome the weakness of SCEs caused by their narrow band gap, small electron effective mass, and a high relative dielectric constant. Multigate architectures represent a very consistent way to reduce SS and DIBL while increasing the ON-state current. In addition, to keep improving the performance of both III–V and Si FETs in the future technology nodes, their source and drain regions should be optimized to minimize their contact series resistance since the overall device performance will be dominated by the contact resistance.

# ACKNOWLEDGMENT

The authors acknowledge the support of the MSD Focus Center, one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity and support from Intel Corporation. The authors would like to thank Dr. T. Rakshit and his colleagues at Intel Corporation and Prof. D. Antoniadis and Prof. J. del Alamo at the *Massachusetts Institute of Technology* for the valuable discussions. The use of computational resources provided by nanoHUB.org operated by the Network for Computational Nanotechnology and funded by NSF is acknowledged. The simulation results presented here can be duplicated in the simulation tool OMEN\_FET on nanoHUB.org [48].

# REFERENCES

- [1] ITRS, International Technology Roadmap for Semiconductors. [Online]. Available: http://www.itrs.net/Links/2010ITRS/

- [2] Y. Q. Wu, R. S. Wang, T. Shen, J. J. Gu, and P. D. Ye, "First experimental demonstration of 100 nm inversion-mode InGaAs FinFET through damage-free sidewall etching," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [3] B. S. Doyle, S. Datta, M. Doczy, S. Hareland, B. Jin, J. Kavalieros, T. Linton, A. Murthy, R. Rios, and R. Chau, "High performance fullydepleted tri-gate CMOS transistors," *IEEE Electron Device Lett.*, vol. 24, no. 4, pp. 263–265, Apr. 2003.

- [4] Y. Xuan, T. Shen, M. Xu, Y. Q. Wu, and Q. D. Ye, "High-performance surface channel In-rich  $In_{0.75}Ga_{0.25}As$  MOSFETs with ALD high- $\kappa$  as gate dielectric," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- [5] R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, and M. Metz, "High-κ/metal-gate stack and its MOSFET characteristics," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 408–410, Jun. 2004.

- [6] I. Lauer and D. A. Antoniadis, "Enhancement of electron mobility in ultrathin-body silicon-on-insulator MOSFETs with uniaxial strain," *IEEE Electron Device Lett.*, vol. 26, no. 5, pp. 314–316, May 2005.

- [7] J. Wang, E. Polizzi, and M. Lundstrom, "A three-dimensional quantum simulation of silicon nanowire transistors with the effective-mass approximation," *J. Appl. Phys.*, vol. 96, no. 4, pp. 2192–2203, Aug. 2004.

- [8] M. Radosavljevic, G. Dewey, J. M. Fastenau, J. Kavalieros, R. Kotlyar, B. Chu-Kung, W. K. Liu, D. Lubyshev, M. Metz, K. Millard, N. Mukherjee, L. Pan, R. Pillarisetty, W. Rachmady, U. Shah, and R. Chau, "Non-planar, multi-gate InGaAs quantum well field effect transistors with high-κ gate dielectric and ultra-scaled gate-to-drain/gate-to-source separation for low power logic applications," in *IEDM Tech. Dig.*, 2010, pp. 6.1.1–6.1.4.

- [9] G. Dewey, R. Kotlyar, M. Radosavljevic, R. Pillarisetty, T. Rakshit, H. Then, and R. Chau, "Logic performance evaluation and transport physics of Schottky-gate III–V compound semiconductor quantum well field effect transistors for power supply voltages (VCC) ranging from 0.5 V to 1.0 V," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [10] S. Oktyabrsky and P. Ye, Fundamentals of III–V Semiconductor MOSFETs. New York: Springer-Verlag, 2010.

- [11] J.-P. Colinge, FinFETs and Other Multi-Gate Transistors. New York: Springer-Verlag, 2007.

- [12] B. Yu, L. Wang, Y. Yuan, P. M. Asbeck, and Y. Taur, "Scaling of nanowire transistors," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 2846– 2858, Nov. 2008.

- [13] M. V. Fischetti, S. Jin, T.-W. Tang, P. Asbeck, Y. Taur, S. E. Laux, and N. Sano, "Scaling MOSFETs to 10 nm: Coulomb effects, source starvation, and virtual source model," in *Proc. 13th IWCE*, May 2009, pp. 1–4.

- [14] G. Klimeck, S. S. Ahmed, H. Bae, N. Kharche, R. Rahman, S. Clark, B. Haley, S. H. Lee, M. Naumov, H. Ryu, F. Saied, M. Prada, M. Korkusinski, and T. B. Boykin, "Atomistic simulation of realistically sized nanodevices using NEMO 3-D-Part I: Models and benchmarks," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2079–2089, Sep. 2007.

- [15] G. Klimeck, S. S. Ahmed, M. Korkusinsk, M. Usman, M. Prada, and T. B. Boikin, "Atomistic simulation of realistically sized nanodevices using NEMO 3-D-Part II: Applications," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2090–2099, Sep. 2007.

- [16] N. Kharche, G. Klimeck, D. Kim, J. A. del Alamo, and M. Luisier, "Multiscale metrology and optimization of ultra-scaled InAs quantum well FETs." *IEEE Trans. Electron Devices*, vol. 58, no. 7, Jul. 2011.

- [17] N. Kharche, G. Klimeck, J. A. del Alamo, and M. Luisier, "Performance analysis of ultra-scaled InAs HEMTs," in *IEDM Tech. Dig.*, 2009, pp. 1–4.

- [18] M. Luisier, N. Neophytou, N. Kharche, and G. Klimeck, "Full-band and atomistic simulation of realistic 40 nm InAs HEMT," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- [19] N. Neophytou, T. Rakshit, and M. Lundstrom, "Performance analysis of 60-nm gate-length III-V InGaAs HEMTs: simulations versus experiments," *IEEE Trans. Electron Devices*, vol. 56, no. 7, pp. 1377–1387, Jul. 2009.

- [20] R. Chau, S. Datta, M. Doczy, B. Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, "Benchmarking nanotechnology for high-performance and low-power logic transistor applications," *IEEE Trans. Nanotechnol.*, vol. 4, no. 2, pp. 153–158, Mar. 2005.

- [21] K. Uchida, T. Krishnamohan, K. C. Y. Saraswat, and Y. Nishi, "Physical mechanisms of electron mobility enhancement in uniaxial stressed MOSFETs and impact of uniaxial stress engineering in ballistic regime," in *IEDM Tech. Dig.*, 2005, pp. 129–132.

- [22] D. A. Antoniadis, A. Khakifirooz, I. Åberg, C. N. Chlirigh, O. Nayfeh, and J. Hoyt, "Channel material innovations for continuing the historical MOSFET performance increase with scaling," *Electrochem. Soc. Trans.*, vol. 3, no. 3, pp. 3–15, Oct. 2006.

- [23] Y. Liu, N. Neophytou, T. Low, G. Klimeck, and M. S. Lundstrom, "Tight-binding study of the ballistic injection velocity for ultrathin-body SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 3, pp. 866–871, Mar. 2008.

- [24] A. Paul, G. Tettamanzi, S. Lee, S. R. Mehrotra, N. Collaert, S. Biesemans, S. Rogge, and G. Klimeck, "Interface trap density metrology from subthreshold transport in highly scaled undoped Si n-FinFETs," *J. Appl. Phys.*, vol. 110, no. 12, pp. 124507–124515, Dec. 2011.

- [25] J.-P. Colinge, "Multiple-gate SOI MOSFETs," Solid State Electron., vol. 48, no. 6, pp. 897–905, Jun. 2004.

- [26] Intel Corporation, Introducing the world's first 3-D transistor ready for high-volume manufacturing, 2011. [Online]. Available: http://www.intel. com/technology/architecture-silicon/22nm/

- [27] M. Luisier and A. Schenk, "Two-dimensional tunneling effects on the leakage current of MOSFETs with single dielectric and high-κ gate stacks," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1494–1501, Jun. 2008.

- [28] M. Luisier, A. Schenk, W. Fichtner, and G. Klimeck, "Atomistic simulation of nanowires in the sp<sup>3</sup> d<sup>5</sup> s\* tight-binding formalism: From boundary conditions to strain calculations," *Phys. Rev. B, Condens. Matter*, vol. 74, no. 20, pp. 205 323–205 334, 2006.

- [29] M. Luisier and G. Klimeck, "Atomistic full-band simulations of silicon nanowire transistors: Effects of electron-phonon scattering," *Phys. Rev. B*, *Condens. Matter*, vol. 80, no. 15, pp. 155 430–155 440, 2009.

- [30] S. Kim, A. Paul, M. Luisier, T. B. Boykin, and G. Klimeck, "Full 3-D quantum transport simulation of interface roughness in silicon nanowire FETs," *IEEE Trans. Electron Devices*, vol. 58, no. 5, pp. 1371–1380, May 2011.

- [31] S. R. Mehrotra, A. Paul, M. Luisier, and G. Klimech, "Atomistic alloy scattering theory in InGaAs: Bulk to ultra-thin-body transistors," unpublished.

- [32] J. Robertsona and B. Falabretti, "Band offsets of high-κ gate oxides on III–V semiconductors," *J. Appl. Phys.*, vol. 100, no. 1, pp. 014111-1–014111-8, Jul. 2006.

- [33] I. Vurgaftmana, J. R. Meyer, and L. R. Ram-Mohan, "Band parameters for III–V compound semiconductors and their alloys," *J. Appl. Phys.*, vol. 89, no. 11, pp. 5815–5875, Jun. 2001.

- [34] M. Bescond, N. Cavassilas, and M. Lannoo, "Effective-mass approach for n-type semiconductor nanowire MOSFETs arbitrarily oriented," *Nanotechnology*, vol. 18, no. 25, pp. 255 201–255 207, Jun. 2007.

- [35] A. Rahman, M. S. Lundstrom, and A. W. Ghosh, "Generalized effective-mass approach for n-type metal-oxide-semiconductor field-effect transistors on arbitrarily oriented wafers," *J. Appl. Phys.*, vol. 97, no. 5, pp. 053702-1–053702-12, Mar. 2005.

- [36] VASP-GROUP, Vienna Ab-initio Simulation Package (VASP) was used in this work. [Online]. Available: http://cms.mpi.univie.ac.at/vasp/

- [37] nanoHUB, NanoHUB.org computational cluster of Two 2.5 GHz 2380 processors was used in this work. [Online]. Available: http://nanohub.org/

- [38] D. A. Antoniadis, private communication, 2011.

- [39] D. J. Frank, Y. Taur, and H. S. P. Wong, "Generalized scale length for 2D effects in MOSFETs," *IEEE Trans. Electron Devices*, vol. 19, no. 10, pp. 385–387, Oct. 1998.

- [40] D. Kim and J. A. del Alamo, "Lateral and vertical scaling of In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs for post-Si-CMOS logic applications," *IEEE Trans. Electron Devices*, vol. 55, no. 10, pp. 2546–2553, Oct. 2008.

- [41] A. Rahman, J. Guo, S. Datta, and M. S. Lundstrom, "Theory of ballistic nanotransistors," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1853– 1864, Sep. 2003.

- [42] H. Pal, "Device physics studies of III-V and Silicon MOSFETs for digital logic," Ph.D. dissertation, Purdue Univ., West Lafayette, IN.

- [43] M. Lusier, "Performance comparison of GaSb, strained-Si, and InGaAs double-gate ultrathin-body n-FET," *IEEE Electron Device Lett.*, vol. 32, no. 12, pp. 1686–1688, Dec. 2011.

- [44] C. L. Hinkel, E. M. Vogel, P. D. Ye, and R. M. Wallace, "Interfacial chemistry of oxides on  $\operatorname{In}_x\operatorname{Ga}_{(1-x)}\operatorname{As}$  and implications for MOSFET applications," *Current Opinion Solid State Mater. Sci.*, vol. 15, no. 5, pp. 188–207, Oct. 2011.

- [45] A. M. Crook, E. Lind, Z. Griffth, M. J. W. Rodwell, J. D. Zimmerman, A. C. Gossard, and S. R. Bank, "Low resistance, nonalloyed Ohmic contacts to InGaAs," *Appl. Phys. Lett.*, vol. 91, no. 19, pp. 192114-1– 192114-3, Oct. 2007.

- [46] R. A. Kubaik, J. J. Haris, and P. Dawson, "Electrical and optical properties of Si- and Sn-doped  $In_xGa_{1-x}As(x \cong 0.53)$  grown by molecular beam epitaxy," *J. Appl. Phys.*, vol. 55, no. 2, pp. 598–600, Jan. 1984.

- [47] S. H. Park, H.-H. Park, M. S. Jelodar, S. Steiger, M. Povolotsky, T. Kubis, and G. Klimeck, "Contact modeling and analysis of InAs HEMT transistors," in *Proc. IEEE Nanotechnol. Mater. Device Conf.*, Oct. 18–21, 2011, pp. 376–379.

- [48] N. Kharche, M. Luisier, G. A. Howlett, G. Klimeck, and M. Salmani-Jelodar, OMEN\_FET. West Lafayette, IN: Purdue Univ., 2011.